Warum ein Bussystem?Die verschieden Komponenten eines Computersystems sollen miteinander kommunizieren können:

|

|

| Komponenten direkt verbinden | Verbinden über Bus-System | ||

|---|---|---|---|

|

|

||

| Vorteile | Die Komponenten können direkt miteinander kommunizieren. | Vorteile | Wenig Leitungen, Anschlüsse |

| Nachteile | Viele Leitungen nötig Viele Anschlüsse an den Komponenten |

Nachteile | Komponenten können nur nacheinander Information übertragen. Kommunikation muss geregelt werden (Protokoll) |

| Beispiele | Switch PS2 Anschlüsse für Maus, Tastatur |

Beispiele | CB-Funk (Walkie Talkie) USB -Maus und -Tastatur |

Busse im (Mikro-) Computer

Bei einfachen Systemen übernimmt die CPU die Rolle des Bus-Masters und steuert die Kommunikation. Der Bus besteht aus drei logischen Bestandteilen.

| Bezeichnung | Aufgabe des Busses | Beispiele für Leitungsbezeichnung |

|---|---|---|

| Daten-Bus | Transport der Daten | D7..D0 |

| Adress-Bus | Adressierung der Komponenten | A15..A0 |

| Steuer-Bus | Steuerung der Kommunikation | R/W, Reset, IRQ, ... |

Die Daten sind hier Byteweise in den Komponenten ansprechbar (8Bit-Datenbus). Jedes Datenbyte bekommt eine eindeutige Adresse. Typischerweise werden den Komponenten Adressbereiche zugeordnet.

Lesen von Daten aus Komponente

Lesen von Daten aus Komponente

- Die CPU legt die Adresse des Datenbytes auf den Adressbus

- Ein CS (Chip-Select) Signal aktiviert die Komponente

- Die Komponente legt die Daten spätestens nach einer Zeit tAA auf den Datenbus

- Die CPU kann die Daten lesen

Schreiben von Daten in Komponente

Schreiben von Daten in Komponente

- Die CPU legt die Adresse des Datenbytes auf den Adressbus

- Ein CS (Chip-Select) Signal aktiviert die Komponente

- Ein Steuerbus-Signal R/!W=0 zeigt an, dass die CPU schreiben will

- Die CPU legt die Daten auf den Datenbus

- Beim steigenden R/!W Signal übernimmt die Komponete die Daten

Daten-Bus: Problem beim Verbinden der Ausgänge

Die Komponenten sollen Daten auch senden können. Bei einfachen Ausgängen kann dies zu Kurzschlüssen führen, ein einfacher Ausgang liefert entweder 0 oder 1.Bei unterschiedlichen Ausgangssignalen "zieht einer nach unten und der andere nach oben". Neben erhöhtem Strombedarf ist der Wert des resultierenden Signals ungewiss.

Open Collector Ausgänge mit PullUp-Widerstand

Open Collector Ausgänge mit PullUp-Widerstand

Der Ausgang liefert entweder 0 oder ist offen (Hochohmig). Ein gemeinsamer PullUp-Widerstand aller Ausgänge zieht in diesem Fall die Leitung nach 1.

Nachteil: Signalwechsel von 0 -> 1 sind langsam wegen rel. grossem PullUp-Widerstand

Tri-State Ausgänge mit Treibern

| EN | X | Q |

|---|---|---|

| 0 | 0 | Hochohmig |

| 0 | 1 | Hochohmig |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Durch einen dritten Hochohmigen Zustand (Klappe halten) können Ausgänge ohne Gefahr von Kurzschlüssen zusammen geschaltet werden. Ein Eingang EN (Enable) steuert ob der Ausgang aktiv ist.

![]()

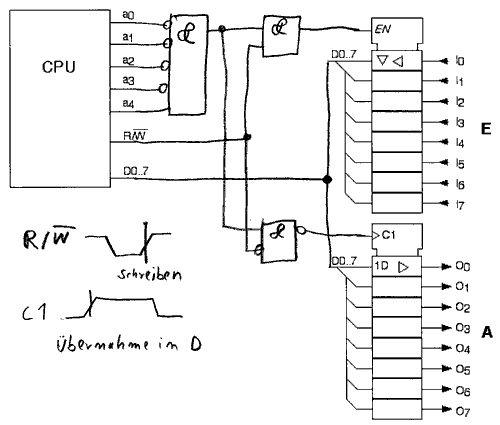

Einfacher Parallel-I/O-Port

Der Microcomputer benötigt eine Ein-Ausgabe-Einheit. Diese Einheit soll unter der Adresse 0x10 (1016) angesprochen werden. Beim Lesen R/!W=1 sollen die Eingänge I0..I7 auf den Adressbus gelegt werden. Beim Schreiben R/!W=0->1 sollen die Daten der CPU in die Ausgänge O0..O7 übernommen werden.

Welche Werte haben die Adressleitungen a0..a4 bei der Adresse 0x10? Entwicken Sie einen Decoder, der genau bei der Adresse 0x10 ein CS (Chip-Selekt) Signal erzeugt.

Schliessen Sie den Eingang mit einer geeigneten Logikschaltung an die CPU an.

Verbinden Sie die CPU mit dem Ausgangs-Baustein. Die Daten der CPU sollen bei steigender Flanke der R/!W Leitung übernommen werden.

Warum ist die Ausgabe als Flankengetriggertes D-Flip-Flop ausgeführt?

Damit der Ausgang stabil bleibt bis zum nächsten schreibenden Zugriff. Wäre es nur ein Treiber, wäre der Ausgang hochohmig.

Adressierung innerhalb der Komponenten

Beispiel 8 Byte RAM: Jede der Speicherzellen enthält einen Buchstaben. Um die einzelnen Speicherzellen ansprechen zu können, muss dem Baustein die jeweilige Adresse der Speicherzelle mitgeteilt werden. Dazu verfügt er über 3 Adress-Eingänge A0..A2.

Beispiel 8 Byte RAM: Jede der Speicherzellen enthält einen Buchstaben. Um die einzelnen Speicherzellen ansprechen zu können, muss dem Baustein die jeweilige Adresse der Speicherzelle mitgeteilt werden. Dazu verfügt er über 3 Adress-Eingänge A0..A2.

Der EN-Eingang aktiviert den Baustein. Somit ist es möglich, mehrere Bausteine parallel an den Bus anzuschliessen und nur jeweils einen Baustein auszuwählen.

Der R/W-Eingang bestimmt die Richtung der Daten: "Lesen vom" oder "Schreiben in" das RAM

Die Auswahl der Adressen im Baustein geschieht über den Adress-Bus.

Die Auswahl des aktiven Bausteins kann über den Adress-Bus (Anordnung der Bausteine im Adressraum) oder Steuer-Bus (spezielle Steuerleitungen die speziell die Peripherie ansprechen) erfolgen.

Es gibt Prozessor-Architekturen, die zwischen Speicher-Adresse und Peripherie-Adresse unterscheiden.