|

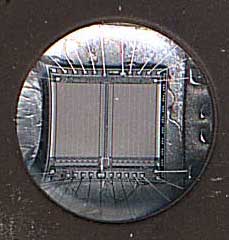

Sicht von aussenWeil man so schön reinschauen kann, habe ich ein altes EPROM (Elektrisch programmierbares Rom, das mit UV-Licht löschbar ist) gewählt.

|

|

Wie viele Adressen hat obiger Speicher-Baustein? 214 = 16384 = 16k Adressen. Wie groß ist der Speicher (Byte/Bit)? Der Speicher ist byteweise organisiert, d.h. zu jeder Adresse werden 8Bit = 1 Byte ausgegeben. Somit hat er 16k Byte das sind 128 k Bit. Die Größe von Speichern werden meist in Bit angegeben: "tms27c128"

|

Sicht von innen (Organisation der Speicherzellen)

Speicherzellen auswählen -> Speichermatrix

Problem: Ein 16-Bit ROM-Speicher (4-Adressleitungen) soll realisiert werden. Die Speicherzellen haben einen Tri-State-Ausgang, bei EN (Enable) = 1 wird der Inhalt auf den Ausgang legt, sonst ist der Ausgang hochohmig, d.h. praktisch nicht verbunden.

Speicherzelle mit Tri-State-Ausgang. Zugriffszeit sei 1.

![]()

Lösung 1

Ein 16-Fach Adressdekoder spricht jede Speicherzelle einzeln an, dafür braucht er die Zeit 1.

Betrachten wir nun die Kosten für diese Lösung: Fläche-Kosten 4*16 = 64, Zugriffszeit 2 gesamt.

Lösung 2

4-Fach-Adressdekoder, 4-Fach-Multiplexer

4-Fach-Adressdekoder, 4-Fach-Multiplexer

ROM-Speichermatrix: Fläche-Kosten 2*4 + 3*4 = 8 + 12 = 20, Zugriffszeit 2 gesamt.

IC-Pins sparen mit RAS/CAS

Angenommen, wir wollen einen 1MBit-Speicher, wieviele Adressleitungen bräuchte der Baustein?

Lösung: 20 Adressleitungen. Wie kann man den Speicher trotzdem in einem 18-Pol-Gehäuse unterbringen?

Lösung: Das IC hat 10 Adresseingänge einen RAS (Row-Address-Strobe) und einen CAS (Column-Address-Strobe) Eingang.

Zuerst wird die Adresse für die Zeile angelegt und RAS gesetzt, der Zeilendecoder ist nun als Latch ausgeführt und kann sich die Zeilenadresse merken.

RAS wird zurückgesetzt. Dann wird die Adresse für die Spalte angelegt und CAS gesetzt, Der Spaltendecoder selektiert die entsprechende Spalte.

Technologie der Speicherzellen

ROM (nicht flüchtiger Speicher)

Früher hat man unter ROM den "nur lese Speicher" verstanden. Angesichts von Flash ROM, der wieder beschreibbar ist trifft diese Klassifizierung nicht mehr die technische Realität. Heute versteht man unter ROM einen Speicher der seine Information auch ohne Spannungszufur behält. /wiki/Festwertspeicher

ROM Festwertspeicher (Read Only Memory)

PROM Programmierbarer Festwertspeicher (Programmable ROM)

EPROM Löschbarer programmierbarer Festwertspeicher (Erasable PROM) Floating Gate

EEPROM Elektrisch löschbarer programmierbarer Festwertspeicher (Electrically Erasable PROM)

Welchen Vorteil hat PROM gegenüber von EEPROM? Was wäre ein entsprechendes Einsatzgebiet?

Wie schnell lässt sich ein EEPROM Byte beschreiben, wie schnell lässt es sich lesen?

RAM (flüchtiger Speicher)

Ist Schreib/Lese-Speicher (Random Access Memory).

Der RAM wird flüchtig genannt, weil er ohne Spannung (siehe CMOS-Batterie) seine Information verliert.

SRAM-Speicherzelle

SRAM ist statisches RAM, die Speicherzelle ist mit einem D-Flip-Flop realisiert.

Zum Lesen (Read) wird die R/!W Leitung auf 1 gelegt, bei EN=1 wird der Ausgang Q des D-Flip-Flops auf Din/out durchgeschaltet.

Zum Schreiben (Write) wird die R/!W Leitung auf 0 gelegt, bei EN=1 ist nun C1 des D-Flip-Flops = 1, folglich wird Din/out gespeichert.

Für eine SRAM-Speicherzelle werden ca. 6 Transistoren benötigt.

Achtung: SRAM-Speicherzelle kann nicht obiger ROM-Speichermatrix verwendet werden. Warum? Wie müsste die Speicher-Matrix verändert werden?

DRAM-Speicherzelle

DRAM-Speicherzelle

Es ist möglich, eine Speicherzelle aus einem Transistor und einem Kondensator zu bauen, das spart viel Platz, ca. 1/4 SRAM. DRAM

Der Nachteil dabei ist, dass sich der Kondensator entläd und daher ständig wieder aufgefrischt werden muss (Refresh).

Die Zeilen werden dazu periodisch ausgelesen und wieder zurückgeschrieben (Refresh-Zyklus).

Würden Sie in einem Handy DRAM oder SRAM einsetzen? Warum?

Wie schnell lässt sich SRAM lesen/schreiben und DRAM lesen/schreiben?

Organisation von Speicherbausteinen zu Modulen

Bisher haben wir den Aufbau von 1 Bit Speicher-Chips betrachtet, d.h. Chips die nur eine Datenleitung besitzen. Wie werden daraus die heutigen Speichermodule mit z.B. 256 MByte gebaut? Externer Link zu CT: Aufbau eines Speichermoduls

Fachchinesisch: Speicherbank, SIMM, RIMM, DIMM, SDRAM, EDO... Speichermodule Historisch: VRAM

Typische Merkmale von alten Speichertechnologien

| Eigenschaft Beispiel |

ROM Maskenprogrammiert |

PROM TBP28SA46 |

EPROM 27C128 |

EEPROM | Flash ROM TMS28F010A |

Nonvolatile SRAM bq4013/Y |

SRAM Cache Register |

DRAM TMS416160 |

|---|---|---|---|---|---|---|---|---|

| Speichergrösse | 512 x 8-Bit | 16k x 8-Bit | 128k x 8-Bit | 128k x 8-Bit | 1 M x 16-Bit | |||

| Flüchtig | - | - | - | - | - | - | X | X |

| Wiederbeschreibbar | - | - | X | X | X | X | X | X |

| Strom-/ Leistungsbedarf bei 5 V |

100 mA | Active 158 mW max Standby 1,4 mW |

55 mW - 165 mW | Active 75 mA | hoch | 1W | ||

| Lesegeschwindigkeit | 35 ns | 120 ns - 250 ns (je nach Typ) |

100 ns - 170 ns | 70 ns - 120 ns | schnell | 60 ns - 80 ns | ||

| Schreibgeschwindigkeit pro Byte | - | 20 µs | ca. | > 16 µs | 70 ns - 120 ns | schnell | 60 ns - 80 ns | |

| Wie oft beschreibbar? | 0 | 1 | 100-200 | 100 000 | 1000 - 10000 | ∞ | ∞ | ∞ |

| Merkdauer | ∞ | ∞ | ? | 10 Jahre | 10 Jahre | 10 Jahre eingebaute Lithium Bat. |

solange Spannung |

16 ms - 128 ms dann Refresh |

| Verwendung | Festwertspeicher | Festwertspeicher | Festwertspeicher | Parameter- speicher |

Firmware / Daten / Fotos / Musik | CMOS-RAM | Cache | Hauptspeicher |

Warum wird eigentlich nicht EEPROM als Hauptspeicher eingesetzt?

Welchen Inhalt hat SRAM-Speicher beim Einschalten der Spannung?